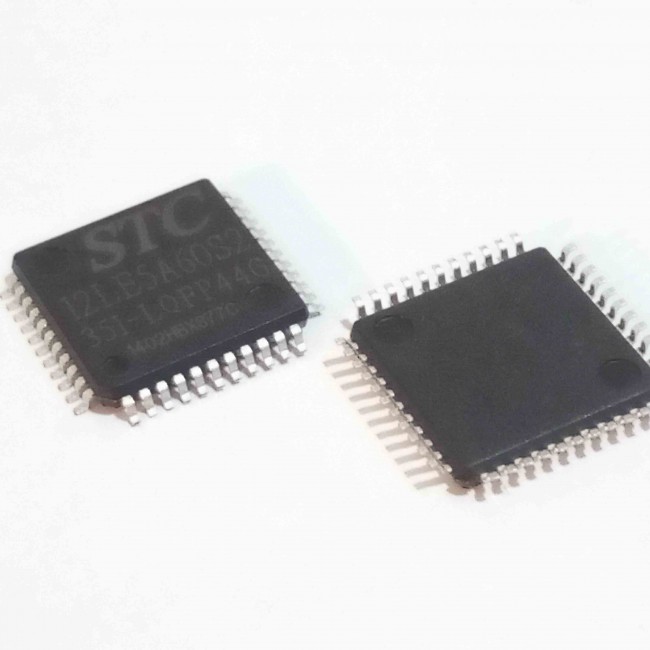

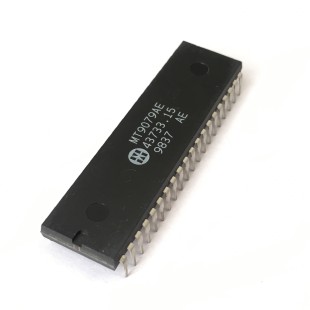

STC12LE5A60S2 35I

STC12C5A60S2, microcontroller based on a high performance 1T architecture 80C51 CPU

- کدکالا:

میکروکنترلر STC12LE5A60S2 مبتنی بر معماری 80C51

دریافت دیتاشیت محصول: Datasheet

STC12C5A60S2 is a single-chip microcontroller based on a high performance 1T architecture 80C51 CPU,

which is produced by STC MCU Limited. With the enhanced kernel, STC12C5A60S2 executes instructions in

1~6 clock cycles (about 6~7 times the rate of a standard 8051 device), and has a fully compatible instruction

set with industrial-standard 80C51 series microcontroller. In-System-Programming (ISP) and In-ApplicationProgramming (IAP) support the users to upgrade the program and data in system. ISP allows the user to download

new code without removing the microcontroller from the actual end product; IAP means that the device can write

non-valatile data in Flash memory while the application program is running. The STC12C5A60S2 retains all features of the standard 80C51. In addition, the STC12C5A60S2 has two extra I/O ports (P4 and P5), a 10-sources,

4-priority-level interrupt structure, 10-bit ADC, two UARTs, on-chip crystal oscillator, a 2-channel PCA and

PWM, SPI, a one-time enabled Watchdog Timer.

Features

Enhanced 80C51 Central Processing Unit ,1T per machine cycle, faster 6~7 times than the rate of a standard 8051.

Operating voltage range: 5.5V ~ 3.5V or 2.2V ~ 3.6V (STC12LE5A60S2).

Operating frequency range: 0- 35MHz, is equivalent to standard 8051:0~420MHz

On-chip 8/16/20/32/40/48/52/56/60/62K FLASH program memory with flexible ISP/IAP capability

On-chip 1280 byte RAM: 256 byte scratch-pad RAM and 1024 bytes of auxiliary RAM

Be capable of addressing up to 64K byte of external RAM

Dual Data Pointer (DPTR) to speed up data movement

Code protection for flash memory access

Excellent noise immunity, very low power consumption

four 16-bit timer/counter, be compatible with Timer0/Timer1 of standard 8051, 2-channel PCA can be available as two timers.

10 vector-address, 4 level priority interrupt capability

One enhanced UART with hardware address-recognition and frame-error detection function

Secondary UART with self baud-rate generator

One 15 bits Watch-Dog-Timer with 8-bit pre-scaler (one-time-enabled)

SPI Master/Slave communication interface

Two channel Programmable Counter Array (PCA)

10-bit, 8-channel Analog-to-Digital Converter (ADC)

Simple internal RC oscillator and external crystal clock

Power control: idle mode(all interrupt can wake up IDLE mode) , power-down mode(external interrupt can

wake up Power-Down mode) and slow down mode

Power down mode can be woken-up by PCA_pin, RXD_pin, T0/T1 pin and external interrupts (INT0, INT1)

44/40/36 programmable I/O ports are available

Programmable clock output Function. T0 output the clock on P3.4,T1 output the clock on P3.5,BRT output the

clock on P1.0

External low-voltage detector function(P4.6, the EA pin at the pin location of standard 8051)

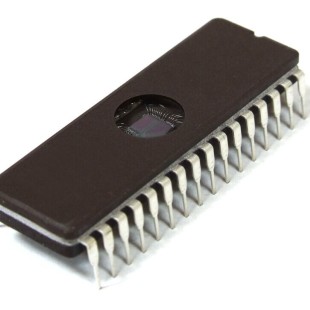

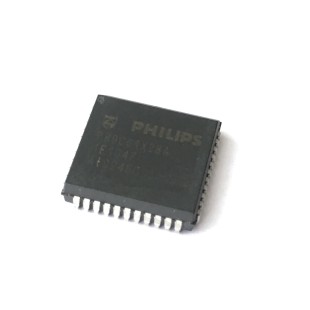

Five package type : LQFP-44, LQFP-48 ,PDIP-40, PLCC-44,QFN-40

- - نشانی ایمیل شما منتشر نخواهد شد.

- - لطفا دیدگاهتان تا حد امکان مربوط به مطلب باشد.

- - لطفا فارسی بنویسید.

- - میخواهید عکس خودتان کنار نظرتان باشد؟ به gravatar.com بروید و عکستان را اضافه کنید.

- - نظرات شما بعد از تایید مدیریت منتشر خواهد شد